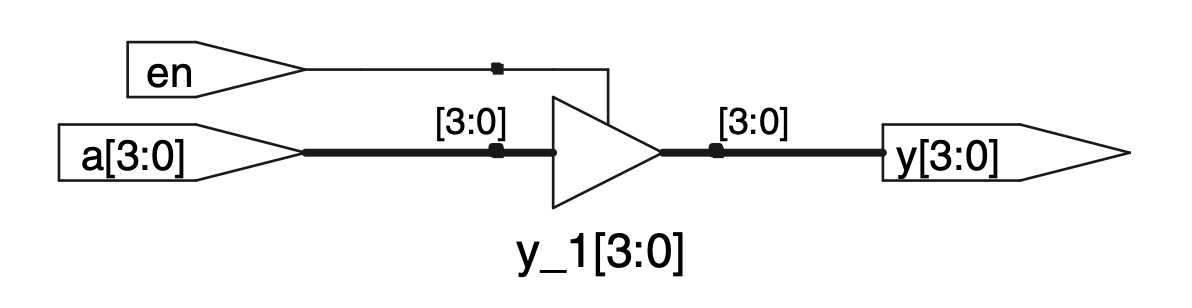

Acts a Buffer which can be Enabled/Disabled

If the buffer is enabled, the output is the same as the input. If the buffer is disabled, the output is assigned a floating value (z)

‘z’ is a floating value when the enable (en) is low, which can be imagined as a broken wire connection.

System Verilog:

module tristate(input logic [3:0] a,

input logic en,

output tri [3:0] y);

assign y = en ? a : 4'bz;

endmodule

Tristate buffers are used when multiple drivers are driving a single net, in this case we cannot use logic. Logic can only have single driver.

If in case a bus is simultaneously driven by multiple tristate buffers where one value is 0 and other is 1, we can have a contention. The result is ‘x’ an invalid logic level

Tristate busses can have multiple drivers, so they should be declared as a net. Two types of nets in SystemVerilog are called tri and trireg. Typically, exactly one driver on a net is active at a time, and the net takes on that value. If no driver is active, a tri floats (z), while a trireg retains the previous value. If no type is specified for an input or output, tri is assumed. Also note that a tri output from a module can be used as a logic input to another module.

Note: if a gate receives a floating input (z) it may produce an output level x as it cannot determine the level.

Source: Digital Design & Computer Architecture by Harris & Harris